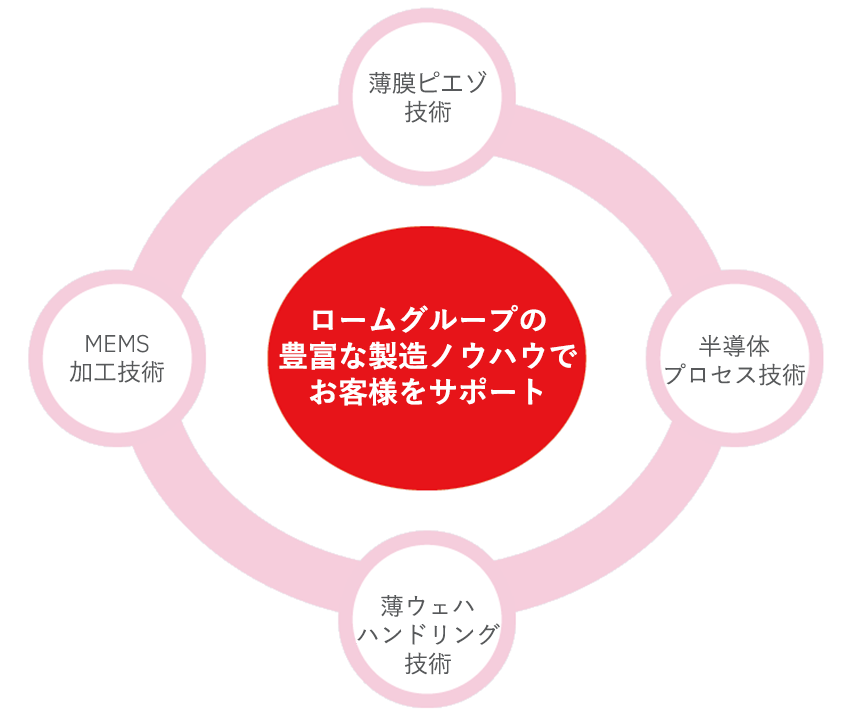

薄膜ピエゾMEMSファウンドリ

開発・量産受託

主な技術・サービス

シリコンウェハやSOIウェハなどを用いたMEMSデバイスのプロセス立案、高性能圧電膜の製造、圧電MEMSデバイスの受託加工や設計サポートなど、試作・開発から量産までをトータルサポートいたします。ホームページやカタログに掲載していない個別プロセスのご相談もお気軽にお問い合わせください

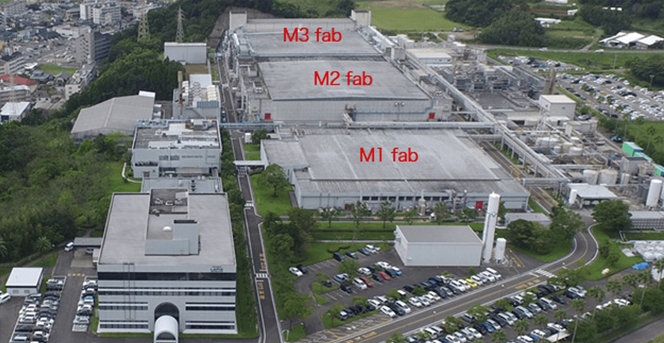

量産・開発ライン

ラピスセミコンダクタ宮崎工場に、独自の薄膜ピエゾ技術とLSI生産ラインを融合した6インチMEMSラインを構築しています。

| 場所 | 宮崎県宮崎市清武町 |

|---|---|

| クリーンルーム | ピエゾMEMS専用部分 1,360m2 |

| クリーン度 | Class 1-1,000 |

| ウェハ径 | 6インチ |

| 提供サービス | 開発サンプル試作、量産 |

| ISO等 | ISO9001, ISO14001 |

| 開発/量産経験 | アクチュエータ、センサ |

| プロセス技術 | PZT圧電薄膜、両面Si加工可能、ウェハ接合 |

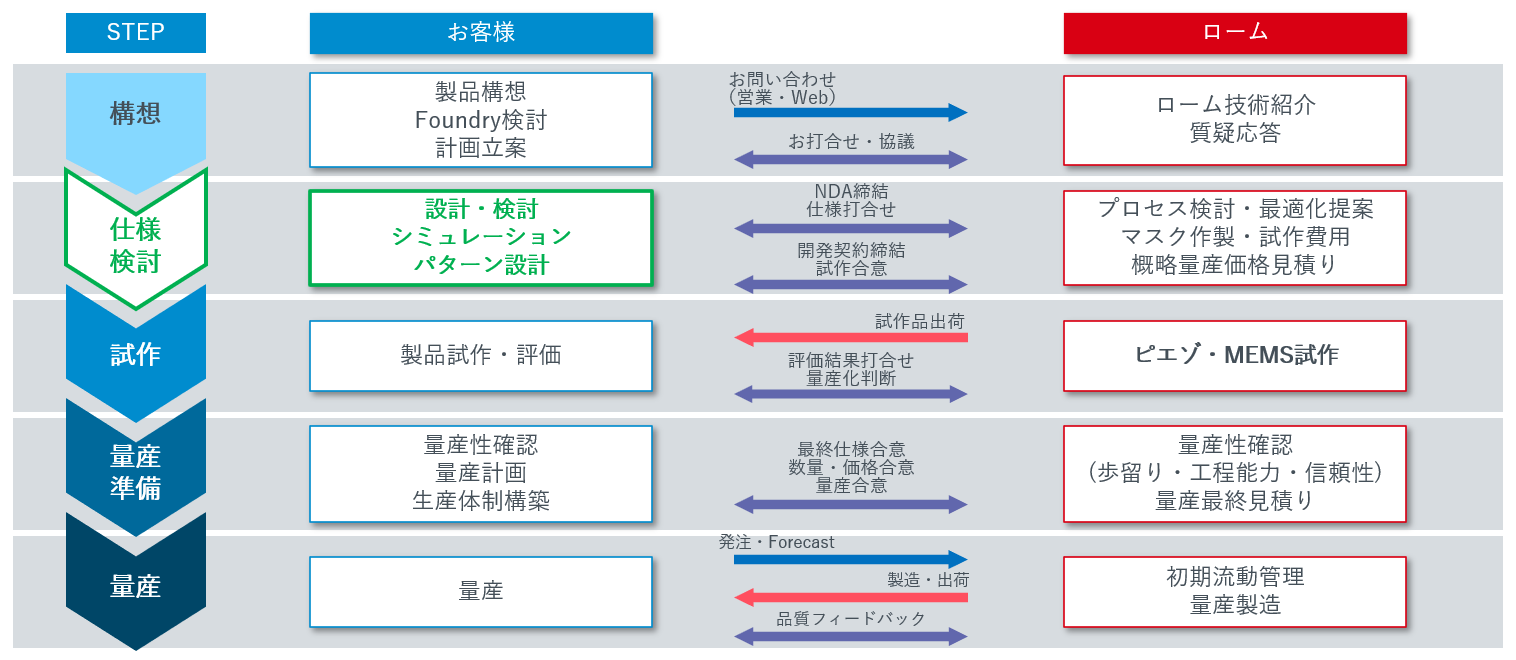

お客様からの相談から量産までの流れ

専用MEMSラインでファウンドリとしてお客様の製品の試作から量産まで対応いたします!

*上記フローは、一般的な例で実際のフローは案件毎に、ご相談の上決定いたします。

ご相談、ご依頼、ご要望については、お問い合せページのフォームに記入いただき、お気軽にお問い合せください。

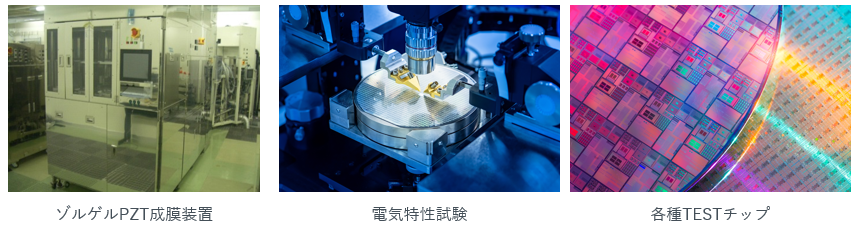

保有設備

MEMSプロセスに必要な設備、解析ツールを製造ライン内に保有していることで、幅広いデバイスのプロセス提案と品質向上へのアプローチが可能です。

| プロセス分類 | 設備 |

|---|---|

| 成膜 | |

| ゾルゲル(PZT系) | |

| PE-CVD (SiO2, SiN) | |

| LP-CVD (SiO2, SiN, poly-Si) | |

| 熱酸化炉 | |

| スパッタ (Pt, Ir, IrO2, AlCu, Ti, TiN 等) | |

| ALD(Atomic Layer Deposition) (Al2O3, SiO2, Ta2O5) |

|

| 撥水コート成膜 | |

| フォトリソグラフィ | |

| 塗布・現像 | |

| MPA (Mirror Projection Aligner) | |

| 両面アライナ、IRステッパ、i線ステッパ | |

| ドライエッチング | |

| Si深堀エッチング | |

| 層間膜RIE装置 | |

| PZT・電極用ICPエッチャ | |

| ウェットエッチング | |

| シリコン酸化膜エッチング | |

| Auエッチング | |

| Si異方性エッチング | |

| ウェハ接合 | |

| 樹脂接合 | |

| 陽極接合 |

| プロセス分類 | 設備 |

|---|---|

| ラミネート | |

| ウェハテープ貼り合せ自動機 (UVテープ、熱剥離シート、ポリイミド等) |

|

| 剥離・洗浄 | |

| アッシャー | |

| 有機・ポリマー剥離 | |

| 酸洗浄、スクラバ | |

| 個片化等 | |

| ダイシング、2流体洗浄 | |

| サークルカットダイサー | |

| 計測関係 | |

| 解析SEM・測長SEM 、イオンミリング | |

| 光学式測長装置 | |

| 表裏ずれ測定装置 | |

| 可視光・IR・レーザー顕微鏡 | |

| X線回折装置 | |

| レーザー式変位測定装置 | |

| 蛍光X線分析装置 | |

| 接針式段差計、光学式干渉段差計 | |

| エリプソメータ | |

| 自動外観検査装置(表裏貫通ウェハ対応) | |

| 各種電気的特性評価装置 (プローバ、テスタ) |

プロセス能力

ホームページやカタログに掲載していない個別プロセスのご相談もお気軽にお問い合わせください。

| 工程 | プロセス仕様 | 数値 | 備考 |

|---|---|---|---|

| フォトリソグラフィ | 最小線幅 (ステッパー使用) 最小線幅 (アライナー使用) |

1μm 3μm |

|

| Si深堀エッチング | テーパー角 エッチングレート面内均一性 寸法精度 |

90±1度 ≦5% ±0.1μm (いずれもパターン依存あり) |

基板貫通加工可 表裏両面加工可 (ノッチフリー) テーパーコントロール可 |

| TMAHエッチング | 深さ | ≦面内5% | 基板貫通加工可 表裏両面加工可 |

| PZT成膜 | 膜厚精度 | ウェハ内 ±1.0% ウェハ、ロット間込み ±2.5% |

ドーピング例 (Nb, La) |

| PZTエッチング | 加工線幅精度 エッチングレート面内均一性 |

±1μm ≦5% (PZT厚さ~3μm、テーパー形状あり) |

Ptストップ可 |

| スパッタ | 膜厚均一性 | ≦面内4% | Pt, Ir, IrO2, AlCu, Ti, TiN 等 |

| CVD | 膜厚均一性 | ≦面内4% | SiO2, SiN |

| ALD | 膜厚均一性 | ≦面内5% | Al2O3, Ta2O5, SiO2 |

| 樹脂接合 | アライメント精度 樹脂厚さ |

±5μm 1~3μm |

エポキシ、BCB |

| 陽極接合 | 封止内部圧力 | >0.01Pa | Si/ガラス |

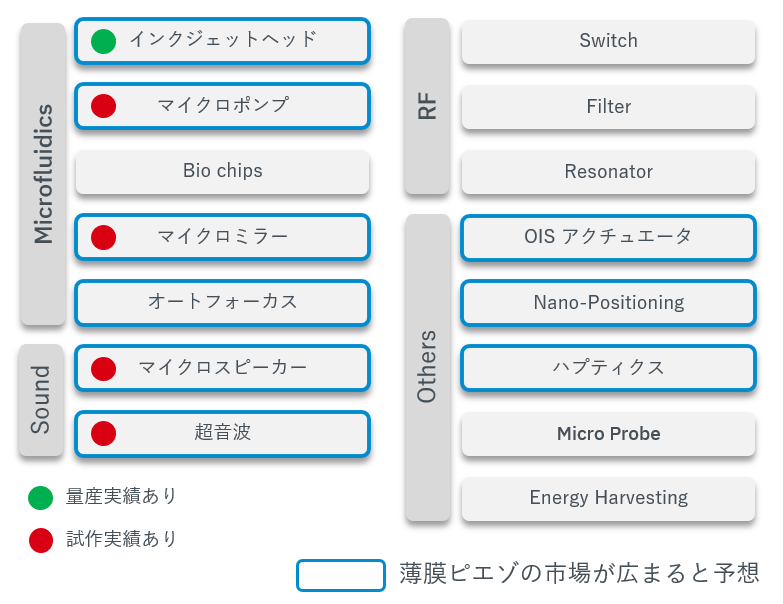

試作・量産実績例

インクジェットヘッドでの量産実績とMEMS技術の研鑽を経て、小型、省電力、高変位を必要とするアクチュエータデバイスをお客様と共同で開発、試作評価を進めております。

プロセス技術例

PZT薄膜の性能

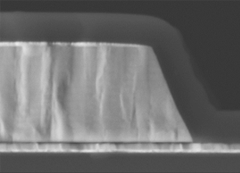

【PZT stack断面】

ロームは1998年に世界で初めて強誘電体メモリの量産化に成功しました。

シリコンウェハでのPZT薄膜利用に関し、長年の経験とノウハウを保有しています。

ローム提供のゾルゲルPZT膜は、自社開発した生産設備で成膜、世界最高レベルの圧電性能と信頼性を実現します。

| 項目 | 値 | 条件 |

|---|---|---|

| 圧電定数: e31,f (-C/m2) | 19 | 10V/μm |

| 逆圧電定数: d31 (-pm/V) | 260 | 10V/μm |

| 絶縁耐圧: (V/μm) | >75 | 室温, (評価電源による制約) |

| 絶縁寿命: (年) | >10 | 20V/μm, 105℃, (加速試験による推定) |

| 繰り返し寿命: (回) | >1x1010 | 10V/μm, 変位10%減 (単極パルス) |

| リーク電流密度: (A/cm2) | <1x10-7 | 20V/μm |

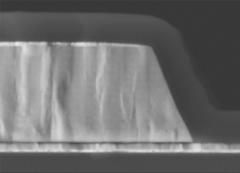

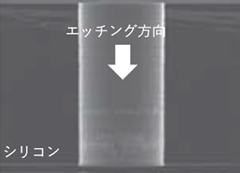

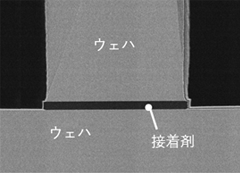

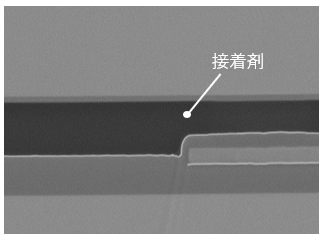

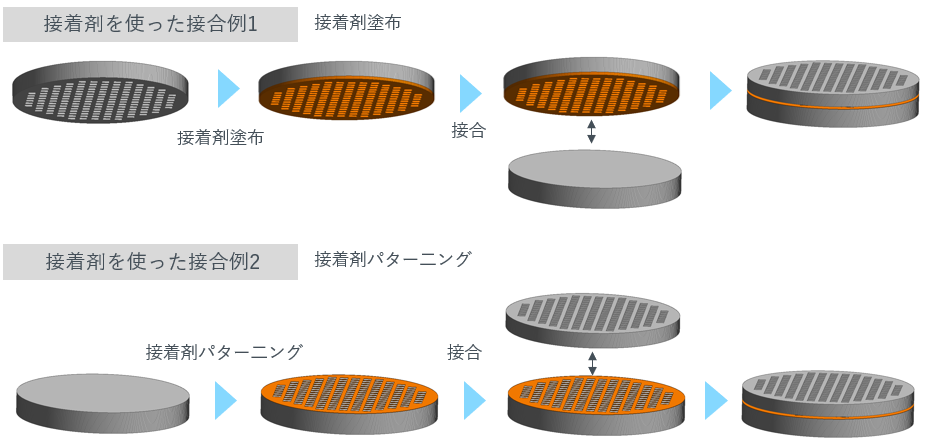

ウェハレベル接合技術

【ウェハ接合断面】

【ウェハ接合断面/段差上】

複数のシリコンウェハ接合技術を保有し、複雑な構造を持つデバイスにおいてもウェハレベルでの接合を実施する事が可能です。

※接着剤塗布・接合プロセスの提案が可能です

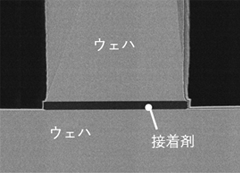

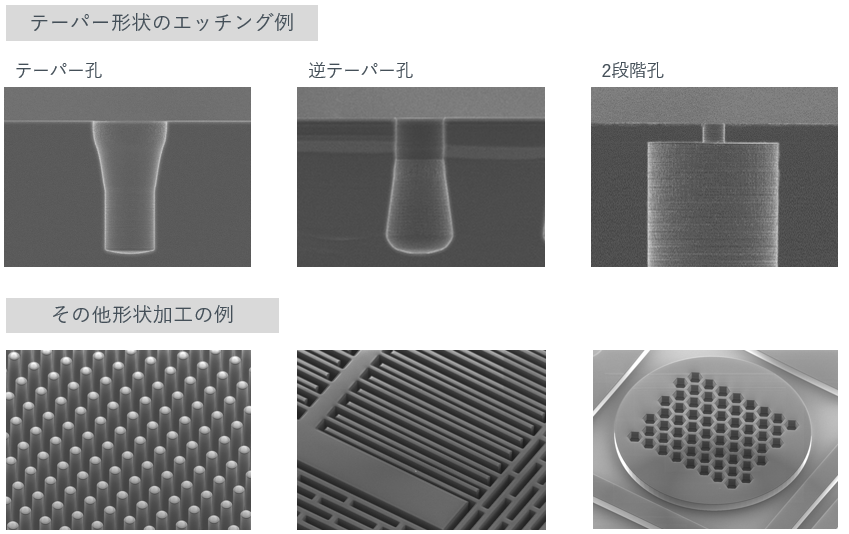

Si深堀エッチング

【400μm Si貫通】

【シリコンウェハ加工】

自社開発を含む複数社のSi深堀エッチング装置を保有し、製品に最適なシリコンエッチングプロセス(形状、公差、異物レベル、コスト)を提案します。

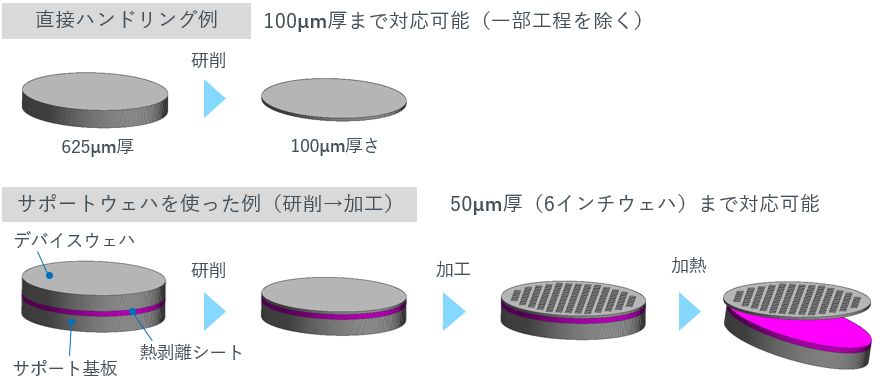

薄ウェハハンドリング技術

【薄いシリコンウェハ】

ウェハの搬送設備を自社開発し、薄いシリコンウェハでのプロセスやウェハ接合が可能となっております。

【TAIKO研削ウェハ】

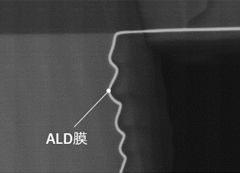

ALD保護膜形成

【シリコン形状断面】

複雑な凹凸形状を持つデバイスにおいても、 *ALDにより均一に保護膜を形成する事が可能です。

*ALD:Atomic Layer Deposition(原子層堆積法)

保護膜・・・外的要因(インク、接触による摩耗、帯電など)からデバイスを守ります。

ALD成膜の詳しい解説はこちら -エレクトロニクス豆知識

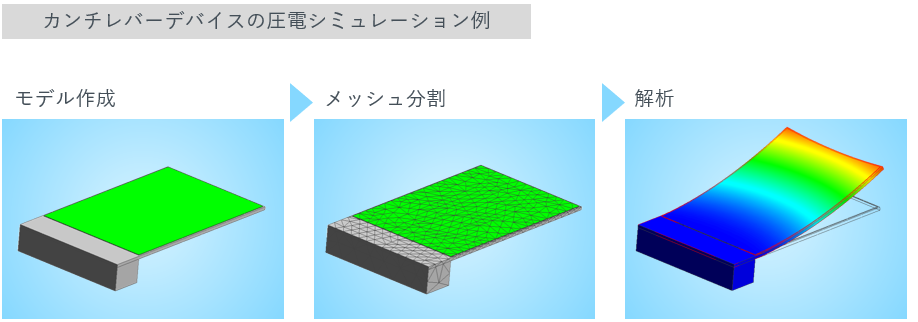

圧電デバイスのシミュレーション解析

【シリコンカンチレバー断面】

圧電デバイスの有限要素シミュレーションを実施し、各種デバイスの最適な構造やプロセスを提案する事が可能です。