ロームは、最小パルス幅が9nsと極めて狭いDC-DCコンバーター制御技術を開発した。「ナノ・パルス・コントロール技術」と呼ぶ。この技術を使えば、2MHzと高いスイッチング周波数でも、48Vの入力電圧を1V近辺の出力電圧に一気に変換できるようになる。制御に不可欠なコイル電流値を事前に入手する「フライングスタート」を導入することで、これまでは30nsだった最小パルス幅を約1/3の9nsまで狭くすることに成功した。

ノイズが元凶

従来、最小パルス幅を狭くできなかった最大の原因は、降圧型DC-DCコンバーター回路に発生するノイズにあった(図3)。同期整流方式の降圧型DC-DCコンバーター回路は、ハイサイドスイッチとローサイドスイッチという2つのスイッチ素子を使用しており、一方のスイッチがPWM信号に合わせてオンからオフに切り替わると、もう一方のスイッチがオフからオンへ切り替わる。その切り替わりのタイミングでノイズが発生する。

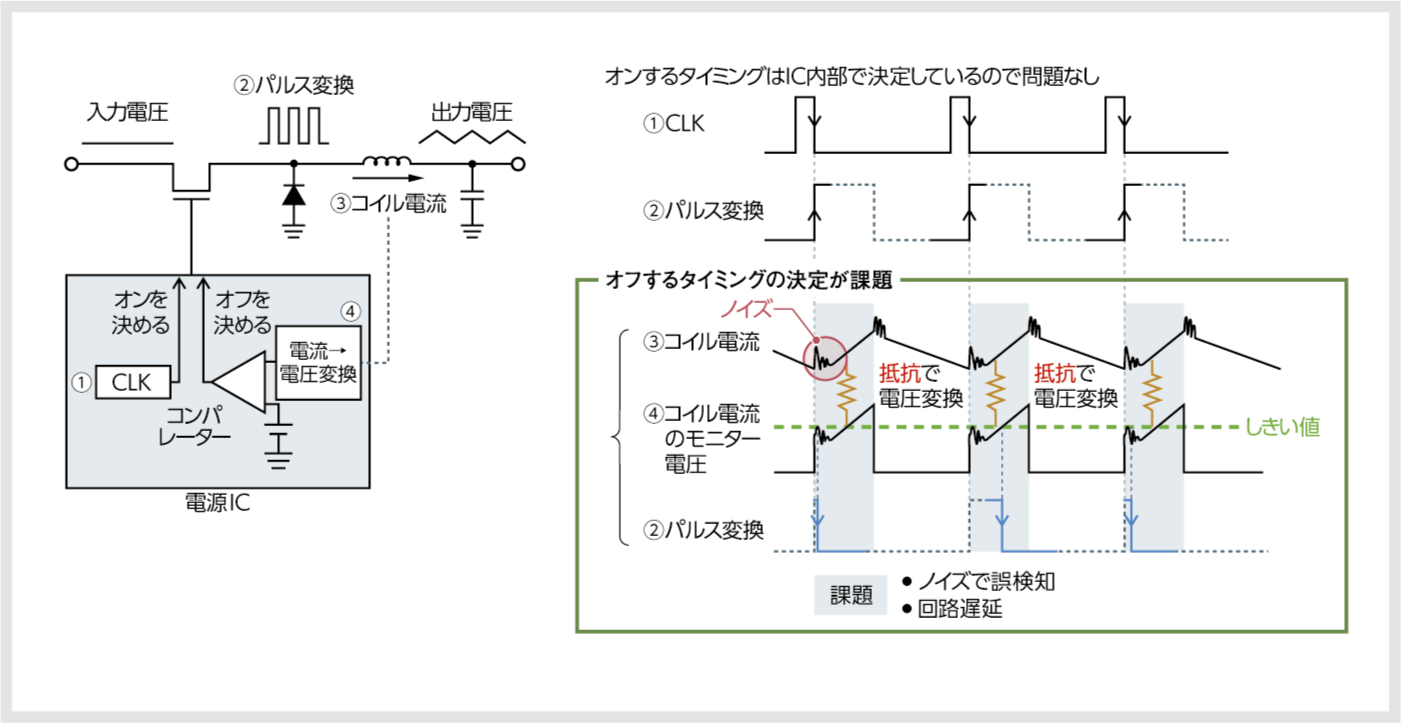

図3 ノイズが発生する理由

配線の寄生インダクタンス成分の逆起電力によってノイズ(リンギング)が発生する。それがコイル電流に重畳するため、コイル電流を検出できなくなっていた。

ノイズの発生源は、配線の寄生インダクタンスである。2つのスイッチ素子とコイルは配線で結ばれている。そこに変化率(di/dt)が大きな電流が流れると、配線の寄生インダクタンスによって逆起電力が発生し、リンギング(ノイズ)が生じる。これが、コイル電流に重畳される。

このノイズがどのような悪影響を及ぼすのか。それを詳しく説明する前に、基本的な情報として降圧型DC-DCコンバーター回路のフィードバックループの制御方式を簡単に説明しておく。一般に、マイコンやFPGAなどのデジタルICに電力を供給する降圧型DC-DCコンバーター回路では、制御方式に「電流モード」を採用するケースが多い。なぜならば、高速な過渡負荷応答特性を達成できるからである。

マイコンやFPGAなどでは、それを搭載した電子機器の消費電力を抑えるため、電子機器の動作状態に応じて小刻みに動作モードを切り替える。このとき、DC-DCコンバーター回路の出力電流が大きく増減することがあり、それに伴って一時的な電源電圧の急激な変化が発生する。過渡負荷応答特性が高いDC-DCコンバーター回路であれば、こうした電源電圧の変化を最小限に抑えられるが、そうでないDC-DCコンバーター回路では、電源電圧の大きな変動を招き、最悪の場合、マイコンやFPGAが定める電源電圧範囲を超えて誤動作を起こす危険性がある。このため、高速な過渡負荷応答特性が得られる電流モード制御方式を採用するのが一般的になっている。

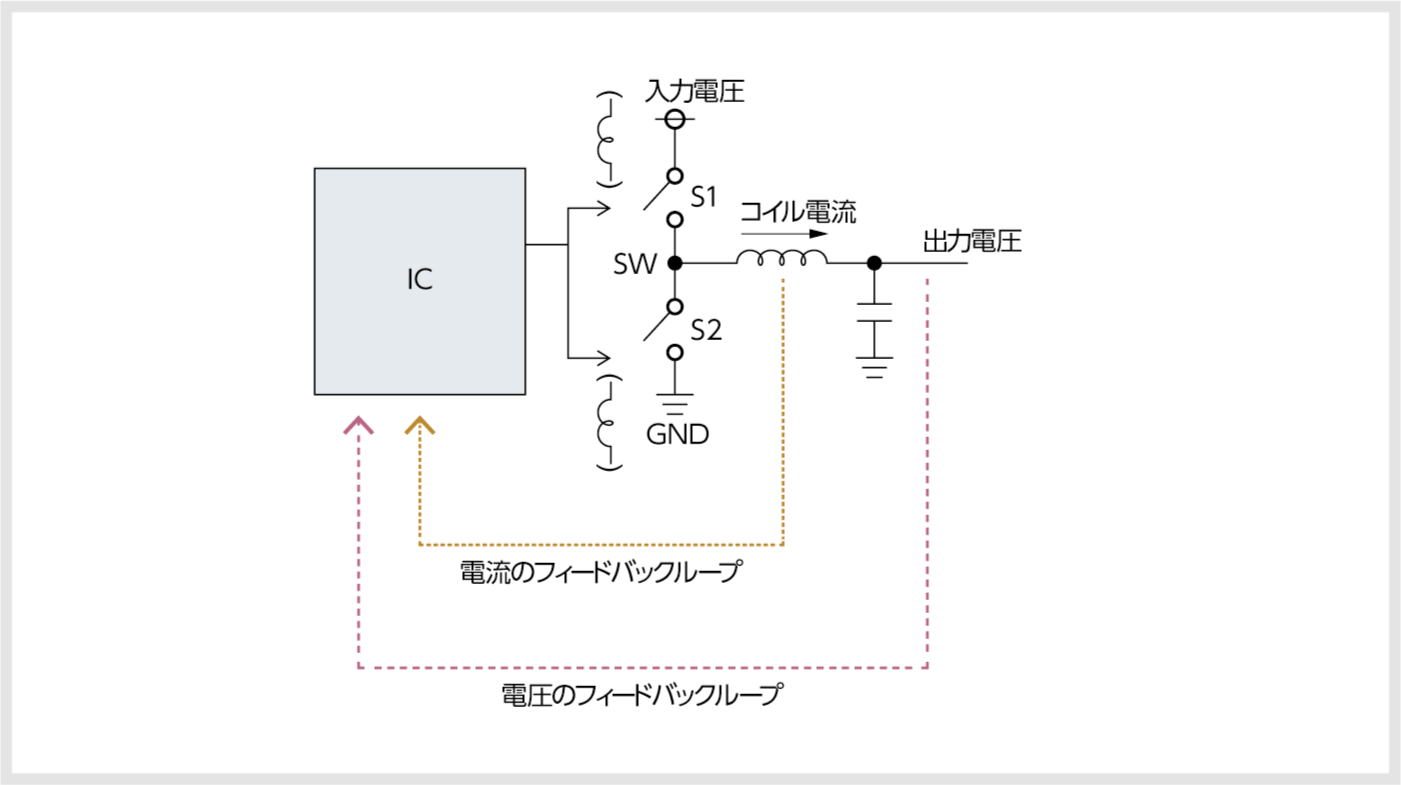

電流モード制御方式は、2つのフィードバックループを持つ(図4)。1つは、出力電圧を検出してフィードバックするループ。もう1つは、コイル電流を検出してフィードバックするループである。

図4 電流モード制御方式

2つのフィードバックループを持つ。出力電圧を検出してフィードバックするループと、コイル電流を検出してフィードバックを掛けるループの2つを使う。

この2つのフィードバックループは連動している。第1のフィードバックループにおいて、検出した出力電圧を誤差増幅器に入力し、基準電圧と比較して差分電圧を生成する。その後、2つ目のフィードバックループで、この差分電圧と、電圧情報に変換したコイル電流を比較することで、PWM信号のパルス幅を決定して出力電圧を安定化させる。

マスク期間+回路遅延

電流モード制御方式では、コイル電流を常時検出し続けることが求められる。通常は、電流検出抵抗を使って、コイル電流を電圧値に変換して検出する。この電圧値と差分電圧と比較して、PWM信号をオフさせるタイミングを決める(図5)。なお、オンさせるタイミングは、降圧型DC-DCコンバーター回路内にあるクロック回路で自動的に決定するため、コイル電流の情報は必要ない。

図5 パルス幅を狭くできなかった2つの理由

1つは、ノイズを避けるためマスクをかけていたこと。もう1つは回路遅延である。

ところがコイル電流には前述の通り、ノイズが重畳されている。この状態のコイル電流を検出すると、ノイズも一緒に拾ってしまうことになり、コイル電流の正確な情報を入手できない。最悪の場合、本来のコイル電流はしきい値を下回っているものの、重畳されたノイズによってしきい値を上回り、予期しないタイミングでPWM信号をオフさせてしまうことが発生しかねない。これでは、出力電圧の安定化制御が実現できなくなる。ノイズ問題は電流モード制御方式の最大の欠点であり、世界中の電源エンジニアが直面している大きな壁だった。

従来は、この問題に対して、ノイズが重畳される期間を避けてコイル電流を検出することで対処していた。具体的には、ノイズの発生期間をマスクし、その直後に電流検出を開始していた。しかも、コイル電流を検出する処理にはある一定時間が必要になる。いわゆる回路遅延である。

つまり、これまで最小パルス幅を狭くできなかった理由は、大きく2つ存在していたことになる(図6)。1つは、ノイズを回避するためにコイル電流を検出するタイミングを意図的に遅らせていたこと。もう1つは、回路遅延である。当社従来品では、ノイズのマスクによって約70nsの遅れ、回路遅延で50ns程度の遅れがあったため、その合計値である120nsが最小パルス幅だった。

図6 スイッチ素子をオン/オフするタイミング

オンするタイミングは、IC内部のクロック(CLK)で自動的に決定する。問題は、オフするタイミングの決定である。