ロームは、最小パルス幅が9nsと極めて狭いDC-DCコンバーター制御技術を開発した。「ナノ・パルス・コントロール技術」と呼ぶ。この技術を使えば、2MHzと高いスイッチング周波数でも、48Vの入力電圧を1V近辺の出力電圧に一気に変換できるようになる。制御に不可欠なコイル電流値を事前に入手する「フライングスタート」を導入することで、これまでは30nsだった最小パルス幅を約1/3の9nsまで狭くすることに成功した。

通信/ネットワーク機器やコンピューター機器、車載用電子機器などで電源電圧を従来の12Vや24Vから、48Vへと高める動きが活発化している。いわゆる「48V化」である。電源電圧を高める最大のメリットは、電力損失の低減にある。供給電力が同じだと仮定すれば、電源電圧を2倍に高めると、電源回路などで生じる電力損失を1/4に低減できる計算になる。

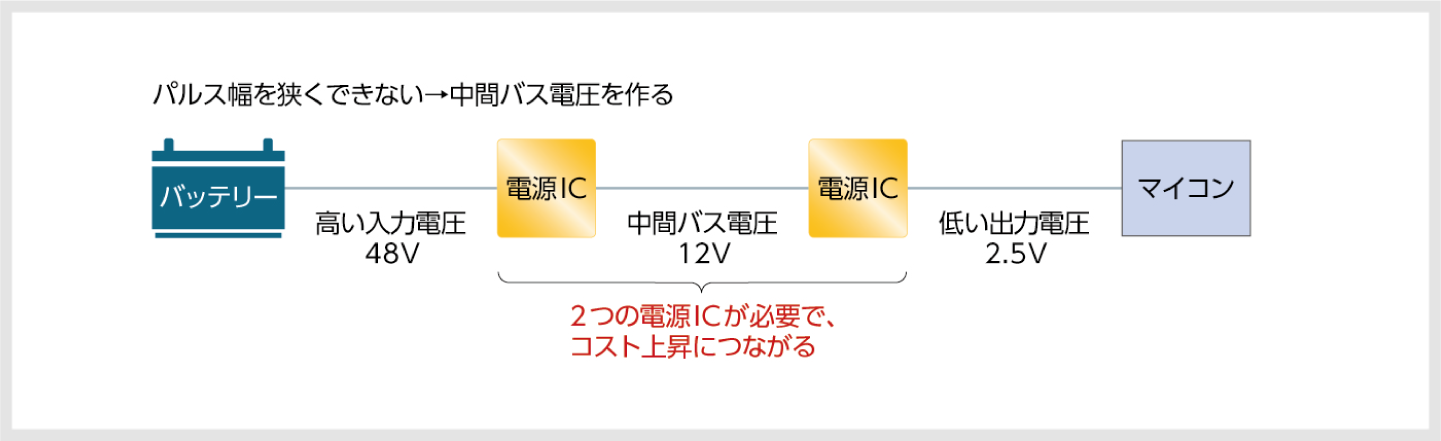

しかし残念ながら、得られるものはメリットだけではない。デメリットもある。最大のデメリットは、電圧の変換回数が増えてしまうことだ。マイコンやFPGA、ASIC、ASSPなどのデジタルICは、製造プロセス技術の微細化に伴って、電源電圧が1Vや1.8V、2.5Vなどへ低下している。電源電圧を48Vに高めれば、デジタルICが必要とする低い電圧に一気に変換することが難しくなる。12Vや9Vといった中間バス電圧を経由する2段階の変換を採用せざるを得ない(図1)。

図1 段階の電圧変換が必要に

従来の車載用DC-DCコンバーターICでは、48Vを2.5Vへと1回で変換できなかった。そのため中間バス電圧を使って、2段階の変換で2.5Vを得ていた。

一般に、電圧変換を実行すれば、電力損失が発生する。変換回数が1回から2回に増えれば、電力損失は約2倍になる。せっかく電源電圧を高めて電力損失を1/4に減らしても、変換回数の増加で電力損失が増えてしまっては、48Vへの移行によって得られるメリットが薄れる。しかも、電圧変換回路が2つになるため、必要になる構成部品も2倍になり、その分だけ部品コストが増加し、プリント基板上の実装面積が大きくなってしまう。

一気に変換できない

48V化のメリットを最大限に活かすには、48Vの電源電圧を1Vや1.8V、2.5Vといった低い電圧に1回で変換できるようにすることが不可欠だろう。しかしこれまでは、技術的な理由から、実現は極めて困難だった。技術的な理由とは、電圧変換回路、すなわちDC-DCコンバーター回路を制御するパルス幅変調(PWM)信号の最小パルス幅を必要なレベルまで狭くできなかったことである。

例えば、2MHzのスイッチング周波数で動作するDC-DCコンバーター回路を使って、48Vを1Vに1回で変換する場合を想定すると、約10nsと極めて狭い最小パルス幅が必要になる。スイッチング周波数を1MHzと半分に減らせば、最小パルス幅は2倍に広げることができるが、それでも約20nsが必要になる。

もちろん、スイッチング周波数をもっと低くすれば、必要となる最小パルス幅はさらに広げられる。しかし、スイッチング周波数を低くすると、外付けのコンデンサーやコイル(インダクター)に大型品が必要になり、DC-DCコンバーター回路の外形寸法が大きくなるという別の問題が発生する。

しかも車載用電子機器では、AMラジオの周波数帯へのノイズ混入を避ける必要がある。AM周波数帯は500k〜1.8MHz程度だ。従って、応用用途における実用性を重視すれば、スイッチング周波数は2MHz以上に設定したいところ。つまり、48Vを1Vに1回で変換するには、10ns程度の最小パルス幅を実現しなければならない。2.5Vへの変換であれば、25ns程度の最小パルス幅が求められる。

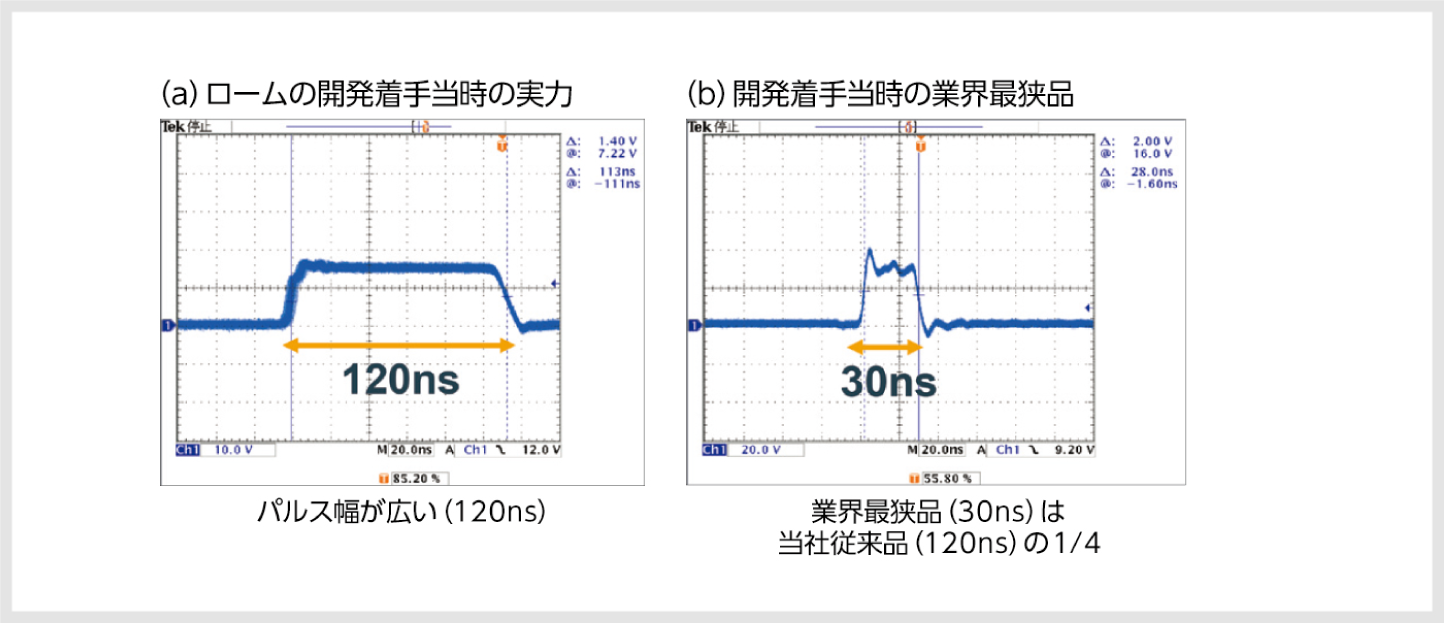

ところが、当社が今回の技術の開発に着手した当時に市場で入手できた一般品の最小パルス幅は最も狭いもので30nsであり、これが従来の限界値だった。いわんや、当社従来品の最小パルス幅は120nsであり、約10nsとは極めて大きな開きがあった(図2)。

図2 業界最狭の最小パルス幅は30nsだった

図右は、最小パルス幅が業界で最も狭い30nsの波形である。図左は、当社従来品の最小パルス幅である120nsの波形だ。

これが、これまで48Vの電源電圧を1Vや1.8V、2.5Vといった低い電圧に一気に変換できなかった最大の理由である。このため、12Vや9V、7Vといった中間バス電圧を利用した2段階の変換を採用せざるを得なかった。