DACDAC 基本形2(バイナリ方式)

そのままデジタル値を受けて動作する回路方式をバイナリ方式と呼びます。

1. バイナリ方式 <抵抗使用の場合>

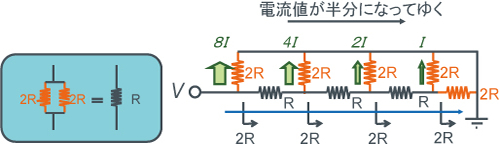

バイナリ方式は、回路構成によりデータに重み付けを持たせたもので、代表例として下図のR-2Rラダー回路があります。

R-2Rラダー回路はどのノードからも抵抗値2Rの並列接続に見えるため、1ノードごとに電流値が半分になってゆきます。

【R-2RラダーDAC例】

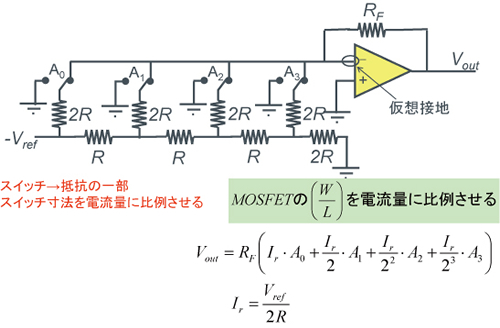

下図は4bitの分解能をもつR-2RラダーDACです。

長所として、分解能10bit程度までDACが小面積で作りやすく(必要な抵抗は、NbitのDACで3N本であり、スイッチも大きくなくてよく、デコーダも不要)、他の方式と組み合わせると、14bit程度までなら実現可能となります。

短所として、抵抗に要求される比精度が高いため、高精度を実現するにはスイッチの工夫(MOSFETのサイズ)や、レイアウト上の工夫(Rと2Rのペア性が重要で、特にMSB側=A0側の抵抗を精度よく作る必要がある)が必要です。

2. バイナリ方式 <キャパシタ使用の場合>

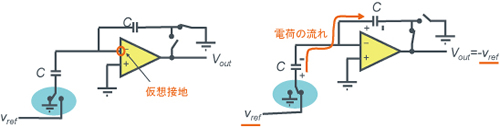

下図はキャパシタ使用のDACの考え方を示すための概念図です。

このDACはスイッチを切り替えながら使う必要があります。

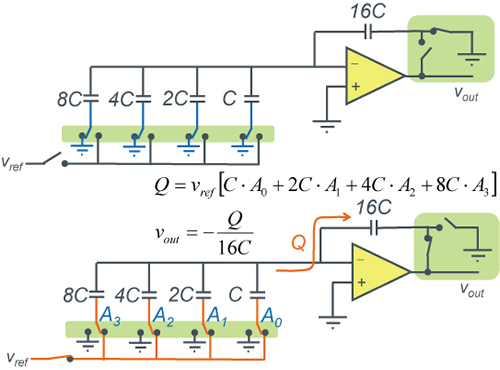

【2NCキャパシタを用いたDAC例】

下図はキャパシタ使用4bit分解能DAC例です。 A0~A3のどのスイッチをVref側に倒すかで、異なるVout電圧を得ることができます。このとき、アンプ右のスイッチ二つが同時にONになると、電荷保存の関係が崩れるため、クロック信号でON時間がオーバーラップしないようにする必要があります。

長所として、キャパシタの比精度が高いので高精度を得やすく、またキャパシタに直流電流が発生しないため、低周波ではアンプ電流のみの低消費電流にできます。

短所は、キャパシタ充放電のため高速化に向かないことと、低速ではリーク電流を補償するためリフレッシュ動作が必要となることです。リフレッシュ制御はリフレッシュ中の出力電圧の維持など工夫が必要です。

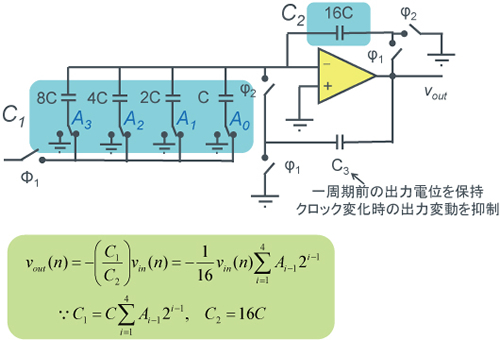

【2NCキャパシタを用いたDAC(リフレッシュ制御あり)例】

リフレッシュ制御を使ったしたCAPA使用の4bitの分解能DACです。

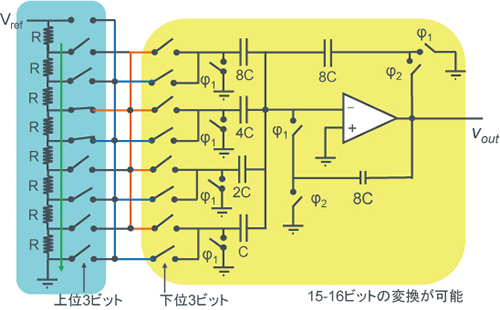

3. バイナリ方式 <抵抗-キャパシタ使用の場合>

【抵抗-キャパシタ混合型 DAC例】

抵抗ストリングDAC部(左)で3bit、キャパシタDAC部で3bit、全体として6bitの分解能を持つ混合型DACです。

上位ビットの抵抗間の電圧を下位のデータにより重み付けして補間します。

高分解能を得ることができるのが特長です。