BD35395FJ-M

1A DDR-SDRAM用 ターミネーション用 リニア電源

BD35395FJ-Mは、JEDEC準拠のDDR1/2/3/3L-SDRAMに対応する、ターミネーション・レギュレータです。N-MOSFETを内蔵しシンク/ソースで最大1Aまで供給できるリニア電源です。内部のOP-AMPを高速設計することで優れた過渡応答特性を実現しています。内部のN-MOSFETを駆動するため、バイアス用電源に、3.3Vもしくは5.0Vが必要です。JEDECで定められた電圧精度を保つために、独立した基準入力ピン(VDDQ)と独立したフィードバックピン(VTTS)を持っており、優れた出力電圧精度、ロードレギュレーションを実現しています。

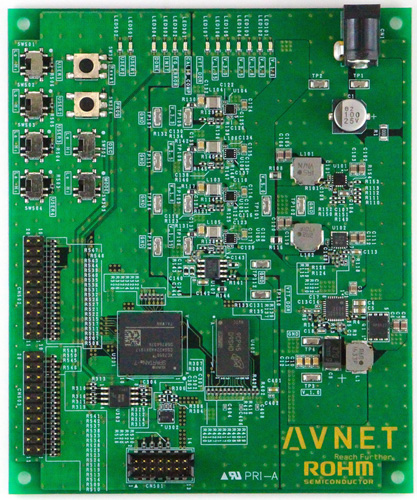

電源リファレンスボード

Xilinx FPGA Spartan-7

主な仕様

特性:

ch

1

Vin(Min.)[V]

2.7

Vin(Max.)[V]

5.5

Iout(Max.)[A]

1

Circuit Current[mA]

2

Thermal Shut-down

Yes

Over Current Protection

Yes

Under Voltage Lock Out

Yes

動作温度範囲(Min.)[℃]

-40

動作温度範囲(Max.)[℃]

105

特長:

· ターミネーション用プシュプル電源内蔵(VTT).· イネイブル機能内蔵

· 低入力誤動作防止回路内蔵(UVLO)

· SOP-J8パッケージ採用:4.9×6.0×1.65(mm)

· 過熱保護回路内蔵(TSD)

· 入力電圧2.7V~5.5V対応

· Dual Channel 対応(DDR1, DDR2, DDR3, DDR3L)

· PGOOD機能内蔵

リファレンスデザイン / アプリケーション評価キット

-

- Reference Design - REFPTR001

- ザイリンクス FPGA Spartan-7 プラットフォームのパワーマネージメント リファレンスデザイン

ロームと電子部品およびエンベデッド・ソリューションの大手商社であるアヴネット株式会社は、ザイリンクスの製品であるFPGA Spartan-7に最適なリファレンス電源を開発しました。 近年、FPGAの電源には高精度な低電圧や複雑な起動シーケンスなどが必要となっています。 一方で設計者には小型化,省電力化,低コスト化など常に設計の更新が要求されており、これらの短期間での実現が課題となっています。ロームでは、FPGA電源として最適な電源のリファレンスデザインを提供することにより、設計者の開発負荷の軽減と市場の要求する性能の達成に貢献します。 今回リファレンスデザインを開発したザイリンクス Spartan-7は、コネクティビティ, センサ フュージョン, エンベデッド ビジョンを活用するインダストリアル, コンシューマアプリケーションに最適です。 ロームのリファレンス電源デザインは、ザイリンクス Spartan-7を安全に起動し、動作確認が取れている電源で構成されています。 リファレンス電源として、応答特性に優れた電源IC「BD95602MUV」、各電源に要求される電流能力を備えた「BD9B305QUZ」,「BD9F500QUZ」,「BD9F800MUZ」およびDDR3L ターミネーション電源「BD35395EFJ-M」を搭載し、入力電圧12VからFPGAの電圧精度仕様を満たす電源電圧を生成すると共に起動時の起動シーケンスにも対応しています。本リファレンスデザインの設計資料として回路図,部品表,基板レイアウトなどの情報がダウンロード可能となっています。

- コネクティビティ, センサ フュージョン, エンベデッド ビジョンを活用するインダストリアル, コンシューマアプリケーション

- 6系統のパワー・ツリーリファレンスデザイン

- XilinxのFPGA Spartan-7向けの12V入力電源ツリーとしてAvnet様と協業開発